Memahami Cara Kerja Rangkaian Full Adder Parallel contohAdd4signed.sch DSCH dalam Operasi Penjumlahan dan pengurangan

DASAR SISTEM #2

Tujuan Praktikum

Memahami cara kerja rangkaian full adder parallel dalam file

“contohAdd4signed.sch” dalam operasi penjumlahan dan pengurangan.

Rumusan Masalah

- Apakah rangkaian full adder parallel telah berfungsi sebagai penjumlahan dan pengurangan?

- Apakah dalam representasinya rangkaian full adder parallel menunjukkan nilai yang overflow? Lalu bagaimana representasinya dalam rangkaian full adder parallel?

- Dalam kondisi apa lampu dapat menyala?

Dasar Teori

1. Penjumlahan (Adder)

Ilustrasi penjumlahan bilangan desimal (kiri) dan bilangan biner (kanan).

|

| Ilustrasi Adder |

2. Penjumlahan Biner 1-Bit

a. Half Adder

Rangkaian penjumlahan yang tidak menyertakan bawaan sebelumnya (previous carry) pada inputnya.

|

| Tabel Kebenaran dan Diagram Digital Half Adder |

b. Full Adder

Rangkaian penjumlahan yang menyertakan bawaan sebelumnya (previous carry) pada inputnya.

|

| Tabel Kebenaran dan Diagram Digital Full Adder |

Dalam

hal ini, Cp adalah previous carry (bawaan sebelumnya) dan Cn

adalah next carry (bawaan

setelahnya). Dari tabel kebenaran terlihat bahwa output S membentuk fungsi

detector jumlah ganjil, dan S dapat diimplementasikan :

Sedangkan untuk menentukan output Cn bias digunakan peta karnaugh,

sehingga Cn dapat diimplementasikan :

c. Full Adder Paralel

Rangkaian logika yang melakukan proses penjumlahan data biner n-bit. Contoh

full adder parallel 4-bit :

|

| Full Adder Paralel 4-bit |

Operasi Full Adder 4-Bit dapat ditunjukkan dalam proses Penjumlahan Sebagai berikut:

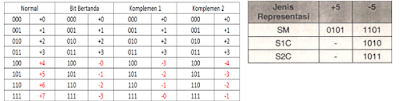

Representasi Operasi Aritmatika (Bit

paling kiri adalah sebagai penanda, 0 positif dan 1 negatif)

|

| Contoh Operasi Full Adder |

Hasil dan Pembahasan

1. Screenshot DSCH

2. Pembahasan

a. Output "7" dan "8" (Uji 1)

|

| Tabel Kebenaran Output "7" dan "8" |

|

| Perhitungan Biner Output "7" dan "8" |

b. Output "b" dan "c" (Uji 2)

|

| Tabel Kebenaran Output "b" dan "c" |

|

| Perhitungan Biner Output "b" dan "c" |

c. Output "E" dan "F" (Uji 3)

|

| Tabel Kebenaran Output "E" dan "F" |

|

| Perhitungan Biner Output "E" dan "F" |

Kesimpulan

- Rangkaian full adder parallel telah berfungsi sebagai penjumlahan dan pengurangan berdasarkan representasi bilangan biner yaitu SM (Signed-Magnitude Representation), S1C (Signed-1’s Complement Representation) dan S2C (Signed-2’s Complement Representation)

- Indikator Overflow adalah apabila dua buah bilangan ditambahkan, keduanya positif atau keduanya negatif, maka overflow akan dan hanya terjadi bila hasilnya memiliki tanda yang berlawanan. Pada ALU, harus memberikan sinyal tentang keadaan ini sehingga tidak terdapat usaha untuk menggunakan hasil operasi tersebut.

- Lampu akan menyala apabila carry out (simpanan) bernilai 1

Daftar Pustaka

Muchlas.

2005. Rangkaian Digital. Gava Media :

Jogjakarta.

Comments

Post a Comment